Timing Violation Fix방법

3탄에 이어 Timing Violation Fix 방법을 설명하도록 하겠습니다.

이해하기 쉽도록 설명하도록 하겠습니다.

그전에 3장을 먼저 읽고 와주세요~

[STA] 3. Setup 과 Hold, Timing Violation

[STA] 3. Setup 과 Hold, Timing Violation

Setup / Hold Timing Check제가 신입때 제일 어려웠던... 머리로는 이해가는데 마음으로는 받아들일수 없었던 setup / hold 개념에 대해 간략하게 소개하도록 하겠습니다. [STA] 1. STA와 Timing Path [STA] 1. STA

vlsiatelier.tistory.com

Setup Violation

Setup Violation을 Fix 하는 방법은 크게 3가지로 나눌 수 있습니다. (그림은 제가 그렸습니다 ㅎㅎ)

(1) Launch Clock을 당긴다. (=빠르게 한다)

(2) Capture Clock을 민다. (=느리게 한다)

(3) Data Path를 줄인다. (=빠르게 한다)

Hold Violation

hold Violation은 Setup과 반대로 생각하면 쉽습니다.

(1) Launch Clock을 민다. (=느리게 한다)

(2) Capture Clock을 당긴다. (=빠르게 한다)

(3) Data Path를 늘린다. (=느리게 한다)

** 추가로 Hold Timing 은 동일 Phase Shift에서 Check한다고 이전 장에서 말씀드렸습니다.

따라서 Clock Skew를 줄이면 Hold Violation Fix에 도움이 됩니다!

Clock을 밀고 당기는건 set_clock_latency라던가 Buffering 등의 방법이 있겠습니다.

set_clock_latency 등 SDC 구문은 아래 글을 참고해 주세요.

https://vlsiatelier.tistory.com/entry/SDC-Synopsys-Design-Constraint

SDC (Synopsys Design Constraint)

SDC (Synopsys Design Constraint)SDC란 VLSI 설계에서 가장 중요한 File 중 하나입니다. 이름에서 알 수 있듯, Synopsys사에서 만든 Format입니다.Clock에 대한 Constraint를 줍니다. 반도체는 Clock이 0 -> 1, 1 -> 0으로

vlsiatelier.tistory.com

Path의 Delay를 추가하거나 뺄 때 모두 Buffer를 사용한 데서 의문이 생길 수 있습니다.

아래 그림을 참고하시면 이해하시기 쉬울것입니다.

A에서 B로 가는 Path가 있습니다. 이 Path에 Buffer를 넣어 Delay를 추가 (느리게) 한다면

위처럼 EndPoint 부근에 Buffer를 추가합니다.

(Buffer로 인한 Drive Stength << Cell Delay)

마찬가지로 Delay를 제거(빠르게) 한다면

StartPoint 부근에 Buffer를 추가합니다.

(Buffer로 인한 Drive Stength >> Cell Delay)

appendix : Clcok 조절과 Side Effect

Clock을 만질 때에는 Side Effect를 조심해야 합니다.

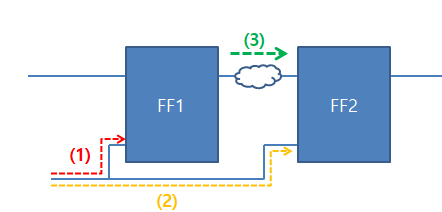

여기 2, 3이라는 FF이 있습니다.

만약 Setup Violation이 발생한다고 가정하겠습니다.

그렇다면

(2)의 Clock을 당기거나 (Launch Clock)

(3)의 Clock을 밀거나 하여 (Capture Clock) Fix 할 수 있을 것입니다.

하지면 고려해야 할 사항이 있습니다.

2,3 FF의 앞 뒤의 1,4 FF에 대해서도 고려해야 합니다.

2,3 관계에서 2 FF의 Clock은 Launch Clock이지만 1,2 관계에서는 2 FF는 Capture Clock이 됩니다.

마찬가지로 2,3 관계에서 3 FF Clock은 Capture Clock 이지만 3,4 관계에서 3 FF는 Launch Clock이 됩니다.

따라서 Clock을 밀고 당길때는 앞/뒤 Clock의 Timing Margin을 보고 판단해야합니다.

'VLSI' 카테고리의 다른 글

| [STA] 5. Slack, Skew, Slew, useful Skew (0) | 2025.02.13 |

|---|---|

| [STA] 3. Setup 과 Hold, Timing Violation (0) | 2025.02.06 |

| [STA] 2. OCV와 CPPR (CRPR) (0) | 2025.02.04 |

| [STA] 1. STA와 Timing Path (0) | 2024.11.27 |

| STA에서 GBA와 PBA (0) | 2024.10.22 |