LEF와 Tech LEF의 차이?

안녕하세요, 익명의 레디입니다.

블로그를 오픈한 지 한 달이 되었는데, 당초 계획보다 자주 찾아뵙지 못했네요. 이 업계의 숙명이지만 과제 시기에는 정말 눈코 뜰 새 없이 바쁘네요. 한가할 때 글을 많이 써둬야겠습니다.

오늘은 VLSI 설계에서 중요한 입력 파일 중 하나인 LEF와 Tech LEF의 차이에 대해 알아보겠습니다.

LEF란?

Library Exchange Format의 약자.

1. LEF란?

Physical 정보를 가지고 있는 ASCII Format의 File입니다. 여기에는 BEOL의 Physical 정보만 담고 있습니다.

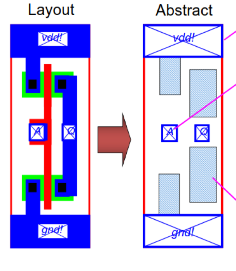

아래 그림에서 Layout(=GDS)는 FEOL과 BEOL 정보를 모두 담고 있습니다. 이 GDS를 Abstract View로 본 것이 LEF입니다.

P&R은 BEOL Level에서만 진행하므로, 사용하지 않는 Front Layer 정보등은 File이 무거워질 뿐입니다. 꼭 필요한 것만 ASCII 형식으로 담은것이 LEF라고 할 수 있겠습니다.

2. LEF의 기원?

LEF 포맷은 1980년대 후반에서 1990년대 초반에 걸쳐 개발되었습니다. 당시 VLSI 설계의 복잡성이 증가하면서, 설계 엔지니어들이 다양한 툴을 사용하여 설계를 완성해야 했습니다. 이 과정에서 물리적 설계 정보를 일관되게 교환할 수 있는 표준화된 형식의 필요성이 대두되었습니다. 이에 따라 LEF 포맷이 등장하게 되었으며, 이는 Cadence Design Systems와 같은 주요 EDA(전자 설계 자동화) 도구 공급업체들이 주도하여 표준으로 자리 잡게 되었습니다.

LEF 포맷은 시간이 지남에 따라 발전하여, 현재는 다양한 세부 정보를 포함할 수 있도록 확장되었습니다. 이는 VLSI 설계의 복잡성을 다루기 위한 필수적인 도구로 자리 잡았으며, 다양한 설계 도구 간의 호환성을 보장하는 중요한 역할을 하고 있습니다.

Tech LEF

간단히 요약하면 공정관련한 LEF입니다.

1. Layer 정보

- 몇장의 Layer를 쓰는지

- 해당 Layer의 Pitch, Width, Spacing, Direction 등

2. Via 정보

- Via Layer, Size

- Name 등

3. Site, Row, Track

- Site : Cell이 놓이는 단위 (세로줄, Cell의 Width 결정, 책장으로 비유하자면 책장의 각 칸의 책꽂이)

- Row : Cell이 놓이는 단위 (가로 줄, Cell의 Height 결정, 책장 자체)

- Track : Routing이 되는 길

Row의 Height는 고정되어있습니다. Site는 Width의 최소한의 단위이므로 해당 Site의 배수로 Cell Width가 결정됩니다.

Track은 Routing이 되는 길인데, Track의 배수로 Row가 결정됩니다.

위 그림에서 H는 Cell의 높이입니다. 이 Cell을 가로지르는 선이 총 8개가 있습니다. 즉 8 Track이 1 Row입니다. 이 Design의 모든 Standard Cell은 8 Track의 높이를 가지고 있습니다.

Cell LEF

Cell의 Physical 정보를 담고 있습니다.

1. Cell Name

- 아래 예시로 보면 'IV'

2. Class

- Cell의 Class (PAD Cell? Core Cell?)

3. Foreign, Origin

4. Size

- x는 3um, y는 12um

5. Site

- 놓일수 있는 Area

6. Pin information

- Name

- Direction(input? Output?)

- Layer

- Shpae (x1 y1 x2 y2)

오늘은 LEF에 대해 알아보았습니다. 실제 Design Kit의 정보를 올릴 수는 없기 때문에, 인터넷에서 검색되는 자료를 바탕으로 작성해 보았습니다. LEF는 'Format'이지만 사용 공정에 따라 일부 다른 내용이 있을 수 있습니다. 참고용으로 봐주시면 되겠습니다.

'VLSI' 카테고리의 다른 글

| Floorplan (0) | 2024.09.12 |

|---|---|

| Post Mask ECO?(Metal ECO) (1) | 2024.07.22 |

| SDC (Synopsys Design Constraint) (1) | 2024.06.05 |

| Back-End(P&R) Flow (0) | 2024.05.29 |

| Physical Design을 하기 위한 Input File. (0) | 2024.05.27 |